# TSOP II

# Thin Small Outline Package Type II

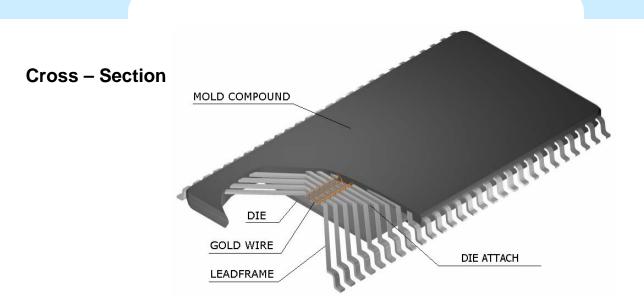

EEMS offers TSOP II package, developped to accommodate devices having the pads at the center of the die: almost all DRAM are designed for a center bond package. Such specific geometry requires the active side of the die is attached to the back of the leadframe: Lead On Chip technology.

EEMS produces high volume of this small and thin package (1.0 mm body thickness), using the Thermoplastic LOC assembly technology and offering a "Full Test Flow", including Burn-In, performed on a large set of "State od the Art" memory testers, suitable for the very high frequency of the last DDR memory generation and above.

In addition, EEMS offers on some dedicated SMT lines the assembly of packaged memory into full tested DIMM Modules, directly pluggable in the end equipment.

The TSOP II packages are available in various pin count and are automatically fully inspected to insure flatness and coplanarity.

#### **Features & Benefits**

- Small board area needed

- Small size

- Cost competitive

- High reliability

- Thermoplastic Lead On Chip tecnology

- Compliant to Rohs directive 2002/95/CE

#### Applications

Memory, memory and memory are the primary users of this package.

#### Device

- SDRAM

- DRAM

- DDR

- All Center Bond Memory

- DIMM

- SIMM

#### **Standard Materials**

Substrate Die Attach Gold wire Mold Compound Lead Solder Plating Packing Packing option AL42 Leadframe LOC Tape 24-30 um Epoxy 85/15 Sn/Pb or 100% Sn Jedec Tray/Tape & Reel Dry Pack

#### End Equipment

- Desktop and Notebook PCs

- Memory Modules

- Telecom Systems

- Industrial Systems

- PC Expansion Cards

#### **Process Highlights**

Processable wafer Die Tickness Bond Pad Pitch Marking Lead inspection 200 – 300 mm 0.280 mm max 60 um min Laser Auto inspection

# TSOP II

## **Specifications**

#### Electrical (simulated w/bondwire)

(10.16 x 22.22 x 1.0 mm body with 66 leads)

| Capacitance (pF) | : 1.0 - 1.6 at 1 GHz   |

|------------------|------------------------|

| Inductance (nH)  | : 2.7 - 5.3 at 1 GHz   |

| Resistance (mΩ)  | : 130 - 270 at 100 Mhz |

## Reliability

| Moisture Sensitivity | : | JEDEC MSL 1 @ up to 260 °C,   |

|----------------------|---|-------------------------------|

| High Temp Storage    | : | 150 °C, 1000 hours            |

| Temp Cycle           | : | -65/+150 °C, 1000 cicles      |

| Temp Humidity Test   | : | 130 °C/85% RH, 240 hours HAST |

| PCT                  | : | 121 °C/2 atm., 240 hours      |

#### Thermal Resistance (simulated)

(12 x 18.4 x 1.0 mm with 48 leads; 1 Watt, 0 m/s airflow as per JEDEC JESD51.2):

$\Theta$  ja = 34 °C/watt Typical

## **Available Services**

- 300 mm wafer full processing

- Wafer backgrinding

- Wafer map / sort

- Product Engineering

- -30 + 125 °C full test

- Dynamic Burn In

- Compliant to Rohs directive 2002/95/CE

- Modules (DIMM) Assembly & Test

| TSOP II Nominal Package Dimensions (mm) |            |            |                   |                   |           |                   |           |  |

|-----------------------------------------|------------|------------|-------------------|-------------------|-----------|-------------------|-----------|--|

| Body Area                               | Lead Count | Lead Pitch | Lead edge to edge | Body<br>Thickness | Stand-off | Overall<br>Height | JEDEC     |  |

| 10.16 x 22.22                           | 86         | 0.50       | 11.76             | 1.00              | 0.10      | 1.2 max           | MS-024 FB |  |

| 10.16 x 22.22                           | 66         | 0.65       | 11.76             | 1.00              | 0.10      | 1.2 max           | MS-024 FC |  |

| 10.16 x 22.22                           | 54         | 0.80       | 11.76             | 1.00              | 0.10      | 1.2 max           | MS-024 FA |  |